# Introduction à la radio numérique

L'article ci-dessous (en deux parties) est d'un niveau technique inhabituel dans notre revue. De nombreux lecteurs le considéreront comme inaccessible. Nous avons cependant estimé qu'il était nécessaire de le publier, et ceci pour plusieurs raisons, Tout d'abord, nous devons dépasser la technicité des années 70, sous peine, de perdre toute crédibilité technique; et Dieu sait que la nôtre est mise en doute par certains. Deuxièmement, un article semblable incitera peut-être ceux de nos collègues qui évoluent ace niveau apublier des articles sur des sujets de même nature, qui se nomment DSP, DDS, spectre étalé... et dont nous trouvons des applications dans tous les équipements commercialisés aujourd'hui. Nous aboutirons, pourquoi pas, à des réalisations à la portée d'un plus grand nombre. Il n'en reste pas moins que des articles de vulgarisation sur ces sujets sont également nécessaires, et nous nous efforcerons de publier ceux que vous voudrez bien nous envoyer. F5RPQ

## F5MI Jean-Pierre Mallet

L'arrivée de circuits intégrés spécialisés nous amène à nous poser de nombreuses questions sur la construction des émetteurs-récepteurs que nous utilisons dans nos stations radioamateurs.

Le concept du super-hétérodyne de papa semble avoir pris un coup de vieux, au regard des techniques actuelles. Aussi me suis-je penché sur un nouveau concept que j'ai appelé radio-numérique. Pour l'instant, je vais me contenter de décrire la partie réception. La partie émission, actuellement à l'étude, fera l'objet d'articles ultérieurs.

La radio est appelée « numérique » par antagonisme avec ce qui se fait actuellement, et qui est de la radio « analogique ». D'un bout à l'autre de la chaîne de réception, le signal est sinusoïdal, possède une valeur finie, et est traité par des amplificateurs plus ou moins linéaires...

En radio numérique, le signal est trans-

formé en une suite de « 0 » et de « 1 » CAN (Convertisseur AnalogiqueNumérique), et ce, le plus près possible de l'antenne. Ce signal numérique est traité par des circuits et ensuite reconverti (comme dans les CDRom audio) en un signal analogique susceptible d'être audible pour nos oreilles. Il est à noter que si la sortie est une sortie digitale pure, le signal numérique ne sera pas reconverti. Un ordinateur se chargera de le traiter (cas du packet-radio).

Quels avantages allons nous tirer de cette modification radicale ?

Les systèmes numériques ne sont pas sujets aux dérives thermiques. Un oscillateur à commande numérique sera infiniment plus stable que son collègue analogique ; la disparition des circuits LC est un avantage majeur.

Les systèmes numériques ne nécessitent aucun réglage. Fini les séances d'accord des circuits FI.

Ils assurent un filtrage très efficace : les filtres FIR (Filtres à réponse Impulsionnelle finie) sont infiniment plus performants que les meilleurs filtres à quartz du commerce.

Enfin, leur reproductibilité est bonne : ceux qui ont peiné pour reproduire tel ou tel montage, paru dans telle ou telle revue, me comprendront. Ils ne sont malgré tout pas parfaits. Comme en analogique, ils peuvent être sensibles au bruit et à l'intermodulation, en raison de l'erreur de quantification et des non-linéarités des CAN et des CNA (Convertisseurs A/N et N/A). L'erreur de quantification dépend de la résolution du système selon la formule : R = 6.02n + 1 .76, où R est le rapport signal/bruit en dB, et n la résolution du système en bits. Le bruit peut être aussi dû à une instabilité de phase de l'horloge du système. Il faut donc soigner au maximum le circuit de l'horloge pour obtenir la meilleure pureté spectrale.

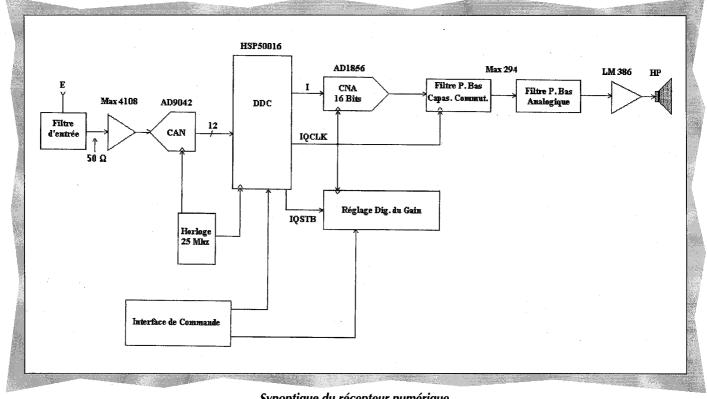

### Synoptique du récepteur numérique.

### FIGURE 1

Une autre dégradation du signal peut survenir au niveau du CNA. Lorsque le signal converti varie dans le temps, des peuvent dépassements fugitifs apparaître lors de transitions de niveau. D'où apparition d'harmoniques au niveau du signal analogique reconstitué. Ce défaut est lié à la conception du convertisseur. Pour apprécier phénomène. on caractérise convertisseur par la marge dynamique entre signal utile et signaux indésirables (SFDR: Spurious Free Dynamic Range) exprimée en dB. Plus cette valeur est élevée, meilleur est le convertisseur.

Enfin, les systèmes numériques sont des dévoreurs d'énergie, ce qui est un inconvénient pour les systèmes portatifs.

Malgré tout, ces défauts sont facilement maîtrisables ; les systèmes numériques sont plus performants que leurs collègues analogiques, le filtrage est on ne peut plus efficace, le rapport signal/bruit est plus élevé, et le risque d'intermodulation est considérablement réduit.

# Constitution d'un récepteur numérique

La figure 1 montre le schéma théorique d'un récepteur numérique. Un filtre d'entrée est accordé sur la fréquence à recevoir ; dans le cas présent, les essais ont portés sur la réception de signaux compris entre 0.5 et 22 MHz (le récepteur pouvant être utilisé comme FI sur 10.7 ou 21.4 MHz pour des récepteurs VHF ou UHF). La gamme dynamique du récepteur étant affectée par la réalisation de ce filtre, on devra soigner sa réalisation. Un amplificateur HF de gain 5 est logé dans cette partie. Pour les fréquences considérées, un ampli opérationnel de style LM733 est très suffisant pour cet usage.

L'amplificateur précédant le CAN est un ampli Maxim, type Max4108, ultra rapide et de très faible distorsion : son SFDR est de 81 dBc à 20 MHz. Il a été configuré pour un gain AC de 11 et pour un gain DC de 1. Les 2 étages peuvent donc donner un gain de 55, ce qui est largement suffisant pour attaquer tous les CAN disponibles sur le marché des convertisseurs A/N.

Le LM733 pouvant être carrément omis dans certains cas.

Toute la gamme dynamique du récepteur repose sur la qualité du CAN qui va être choisi ; ne pas oublier que le prix de revient du CAN varie selon une loi quadratique fonction de sa qualité. Aussi peut-on être amené à dépenser une fortune pour acquérir l'objet de ses rêves ! À l'heure actuelle, il existe plusieurs produits de qualité :

AD 9022 d'Analog Devices : 12 bits 20 MSPS, SFDR = 74 dB à 9.6 MHz, SNR = 65 dB.

- AD 9042 d'Analog Devices : 12 bits 41 MSPS, SFDR = 80 dB à 20 MHz, SNR=68 dB

- HI 5702 de Harris: 10 bits 40 MSPS, SFDR = 63 dB à 10 MHz, SNR = 56 dB. II existe d'autres produits moins performants comme le SPT7855SCS qui est un 10 bits 25 MSPS et le MN5906PD qui est 6 bits flash 35 MSPS mais dont le SNDR n'est que de 35 dB.

Et le prix dans tout cela ? 180 \$ pour un AD9022, 238 \$ pour un AD9042, 330 FF pour un H15702, 110 FF pour le MN5906... Et pour la bête de rêve, un A/D 16 bits fonctionnant à 52 MSPS ? Combien ? le prix d'une Rolls ! Rassurezvous, ça n'existe pas encore sur le marché...

Bon, ces prix vont baisser, Analog Devices annonce pour novembre des versions plastiques à faible coût.

En tenant compte du critère de Nyquist (afin d'éviter le recouvrement des spectres, la fréquence d'échantillonnage doit être au moins le double de la bande passante du signal échantillonné), il est possible de recevoir des signaux légèrement supérieurs à 20 MHz.

Pour recevoir des signaux de fréquence supérieure (75 MHz par exemple), on peut avoir recours à la technique de l'échantilloneur-bloqueur précédant le CAN. Cet étage peut être assimilé à un multiplieur dont l'une des entrées est attaquée par un signal en tout ou rien, riche en harmoniques. Avec une fréquence d'échantillonnage de 20 MSPS (millions d'échantillons par seconde), il y a battement entre l'harmonique 2 (40 MHz) et le signal reçu, ce qui va donner naissance à un signal dont le spectre (autour de 40 - (75 - 40) = 5 MHz) est le symétrique du signal reçu. Ce signal pourra être traité plus facilement par la chaîne numérique ; cette solution respecte le critère de Nyquist. Il suffit que la largeur du spectre du signal traité soit inférieure à la moitié de la fréquence d'échantillonnage, et que l'échantillonneur-bloqueur ait une précision suffisante à 75 MHz. À titre indicatif signalons le AD9101 d'Analog Devices capable de 12 bits à 50 MSPS 75 dB de gamme dynamique, et de 8 bits à 125 MSPS ; 57 dB de gamme dynamique. Le prix de ce produit se situe autour de 600 FF.

il est à noter que tous ces produits sont en provenance directe des États-Unis ; nos amis japonais semblent être (pour le moment !) étrangement absents sur ce marché, pourtant fort prisé par la radio GSM. Se procurer des échantillons en France est possible - à condition d'être un professionnel de l'électronique - mais les prix du change \$ => FF sont très dissuasifs. Il vaut mieux se procurer les produits directement aux US, à condition d'utiliser un moyen de paiement par carte bancaire.

J'utilise pour le moment un AD 9042, avec une fréquence d'échantillonnage de 25 MHz, ce qui limite le fonctionnement du récepteur aux environs de 12 MHz. Alors comment recevoir le 21.4 MHz ? Élémentaire, mon cher Watson ! Il suff it d'utiliser le Sub Sampling !

La fréquence du signal est située entre la moitié et la valeur du signal d'échantillonnage (25 MHz). Le signal sera transposé entre 0 et la moitié de la fréquence d'horloge... L'effet identique à celui que ferait un mélangeur placé entre le filtre d'entrée et le CAN, avec le port LO commandé par la fréquence d'horloge du CAN (25 MHz). Il apparaîtra en sortie vers le DDC un signal qui sera à une fréquence égale à la fréquence d'horloge moins la fréquence du signal d'entrée, et les bandes latérales seront permutées. Ainsi un signal USB de 21.4 MHz apparaîtra au DDC comme un signal LSB de (25 - 21.4 = 3.6 MHz). Les meilleurs résultats que j'aie obtenus avec cette configuration pour une fréquence de 10.7 MHz sont les suivants

- MDS (Signal détectable minimum)=

- -130 dBm.

- IMDDR (gamme dynamique sans distorsion par intermodulation du 31 ordre) = 72 dB.

- BDR (blocage de la gamme dynamique) = 92 dB.

Ces tests sont conformes aux tests définis par le Labo de l'ARRL.

Le convertisseur Analogue/digital est un 12 bits ; les 4 bits de poids faibles n'étant pas transmis, les entrées correspondantes du DDC seront réunies à la masse.

Le DDC (Digital Down Converter) est le cœur numérique du système ; c'est un modèle HSP50016 proposé par Harris. C'est un convertisseur-démodulateur

entièrement numérique réalisé en technologie CMOS, utilisable jusqu'à une fréquence d'échantillonnage de 75 MHz, disponible en boîtier PGA de 48 broches ou dans un boîtier PLCC de 48 broches. Son prix actuel est de 200 \$ pour le modèle 75 MHz.

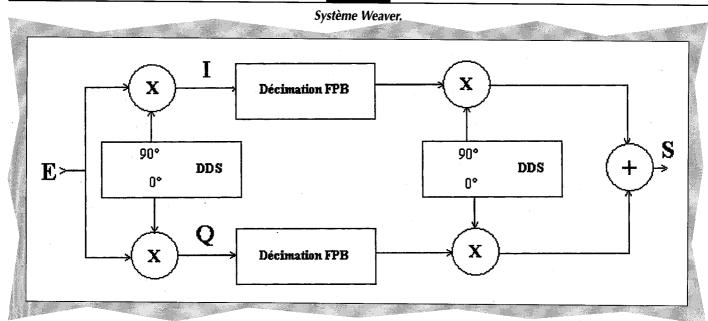

Il permet de réaliser un récepteur SSB selon la méthode de Weaver **f**igure

2) appelée également « la troisième méthode ». Comme le montre la figure, il est constitué d'un générateur de phase très sophistiqué capable de fonctionner selon différents modes: fréquence fixe, saut de fréquence, balayages croissants décroissants. Ce générateur commande un générateur sinusoïdal complexe dont les signaux de sortie en quadrature sont mélangés avec le signal d'entrée. Il en résulte 2 signaux, correspondant à la partie réelle et à la partie imaginaire de la représentation complexe du signal issu du mélange. Ces signaux sont ensuite transmis à une chaîne de traitement qui leur fait subir un filtrage énergique. La plupart des paramètres qui définissent le fonctionnement du circuit sont programmés par écriture dans des registres de contrôle.

La technologie numérique permet l'obtention de performances exceptionnelles :

- Fréquence d'horloge de 0 à 75 MHz.

- Fréquence du signal d'entrée de 0 à la moitié de la fréquence d'horloge soit 0 à 37.5 MHz.

- Résolution en fréquence de l'oscillateur local : meilleure que 0.006 Hz.

- Marge dynamique du modulateur (SFDR) > 102 dB.

#### FIGURE 2

- Ondulation dans la bande passante < 0.04 dB.

- Atténuation hors bande > 106 dB.

- Facteur de forme (de 3 dB à 102 dB) < 1.5.

- Résolution du signal d'entrée 16 bits.

- Fréquence centrale de la bande passante de la sortie fixée à 1 .79 fois la largeur de la bande passante du filtre en mode de sortie réelle.

- Fréquence centrale de la bande passante de la sortie fixée à 0 en mode de sortie quadrature.

performances laissent rêveur. Ajoutons à cela que la programmation du circuit est très facile. Il faut à ce moment rendre hommage à KC1HR PT Anderson, sans qui cette étude n'aurait jamais vu le jour. Reprenons le schéma de la figure 2 , qui est un classique Weaver. La fréquence du premier synthétiseur (oscillateur local) et la bande passante des filtres passe bas est facilement programmable. La fréquence se détermine par le calcul suivant :

FLO = Fporteuse - 1.75 kHz.

Fclk = 25000 kHz.

Phase Incrément 32 bits =

(2^33/Fclk)\*FLO.

Soit à recevoir WWV à 5 MHz.

FLO = 5000 - 1.75 = 4998.25 kHz.

(2^33/25000) \* 4998.25 = 1717385623. Il suffit de transformer ce chiffre en binaire et de l'intégrer dans le registre de contrôle n°1 pour que ce soit effectif. Je ne vous inflige pas la conversion décimal-binaire, mais je vous donne le résultat : 0110 0110 0101 1101 0011 1001 1001 0111.

Le générateur est ainsi une simple table de correspondance; à partir de la valeur de la phase, il produit 2 signaux sinusoïdaux en quadrature, représentés sur 17 bits; ces signaux sont mélangés séparément dans le modulateur avec le signal d'entrée. On obtient représentation complexe du signal issu du battement. On verra en annexe qu'en représentation complexe, un signal modulé occupe un spectre 2 fois moins étendu que sa représentation réelle. Ceci permet de doubler la bande passante du système pour une fréquence d'échantillonnage donnée et d'étendre le domaine d'application d'un circuit numérique limité en rapidité.

Le signal est traité par 2 canaux identiques, l'un correspondant à la partie réelle (l : in-phase), l'autre à la partie imaginaire (Q : quadrature). Chaque canal est constitué de 2 étages, 1 filtre à rapport de décimation élevé (HDF

High Décimation Filter), suivi d'un filtre

FIR à réponse impulsionnelle finie (FIR Finite Impulse Response).

La décimation est un processus par lequel la fréquence d'échantillonnage en sortie de système est égale à un sousmultiple de la fréquence d'échantillonnage en entrée.

Le HDF est constitué d'un Intégrateur suivi d'un filtre en peigne. Ce type de filtre permet l'extraction d'un signal de bande très étroite à partir d'un spectre à large bande. La bande passante d'un tel filtre dépend du rapport décimation compris entre 16 et 32768. Plus ce rapport est élevé, plus la bande passante est étroite. Ce filtre présente aussi une excellente réjection des harmoniques du signal présent à la sortie, ce qui diminue la distorsion. L'atténuation du signal disponible à la sortie du filtre dépend du facteur de décimation. Elle est compensée à l'aide d'un multiplieur à facteur d'échelle programmable.

Le filtre FIR qui suit le HDF est destiné à diminuer les ondulations et à améliorer la réponse en fréquence dans la bande de transition. Il est le siège d'une décimation d'ordre 4 et son efficacité correspond à un filtre à 121 coefficients. La résolution en sortie du filtre est de 18 bits.

La bande passante des filtres est calculée à l'aide des formules suivantes - 3 dB = 0.13957 \* f'.

- 102 dB = 0.19903 \* f'.

où f' = fréquence d'échantillonnage en sortie du filtre HDF (High Decimation Filter).

Sans entrer dans les détails du calcul qui est fort simple et qui conduit à une transformation identique à celle de la fréquence, il est possible de réaliser un filtre SSB de caractéristiques suivantes :

BW à - 3dB : 1954.76 Hz. BW à - 102 dB :2787,535 Hz.

Facteur de forme : 1.426.

Il est possible d'ailleurs de réaliser plusieurs filtres de format divers et de les commuter à la demande!

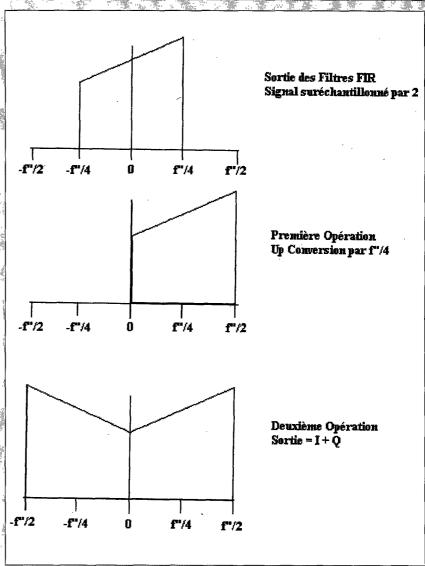

On dispose à la sortie des filtres de 2 en quadrature I et signaux correspondant respectivement partie réelle et à la partie imaginaire du reçu. La fréquence d'échantillonnage f" est défini par : f" = f'/4 = fs/(4 • R), où f" est la fréquence d'échantillonnage en sortie du FIR, f' la fréquence d'échantillonnage en sortie du HDF, et R le rapport de décimation du HDF. Le spectre du signal complexe ainsi obtenu, centré sur la fréquence O, s'étend entre - f"/4 et + f"/4. Ce signal a été obtenu en mélangeant

avant filtrage le signal reçu avec le signal de l'oscillateur local de fréquence FOL. Cette fréquence FOL est centrée sur l'une des bandes latérales du signal reçu. Il est décrit par l'expression : z(n) = cos [2 (F-FOL)n] + jsin [2 (F-FOL)n]

Z(f) = cos [Z(F-FOL)fi] + Jsifi [Z(F FOL)n]

$z(n) = \exp [j2n(F-FOL)]$

Il est possible de convertir ce signal complexe en un signal réel, particulièrement lorsque l'on n'a pas besoin de l'information de phase (démodulation de l'AM, de la SSB, ou de l'ASK).

Pour cela le spectre du signal doit d'abord être décalé de f"/4. Ceci s'obtient en multipliant le signa[ par un signal de fréquence égale au quart de la fréquence d'échantillonnage. Le spectre du signal ainsi obtenu s'étend de la fréquence 0 vers f"/2 (1 seule bande latérale - SSB). En additionnant la partie réelle et la partie imaginaire, on retrouve le signal en représentation réelle (2 bandes latérales - AM). Il est possible de retourner le spectre, soit en mode complexe en accordant oscillateur local sur la bande latérale ad hoc, soit en mode réel en activant la fonction d'inversion spectrale (bit 0 du mot de contrôle 4), réalisant ainsi l'inversion LSB/USB.

La fréquence du second synthétiseur (oscillateur Weaver) est fixée à 1.79 fois la fréquence centrale du filtre. Les deuxièmes mélangeurs, deuxièmes synthétiseurs, et sommateur final supprimés leurs peuvent être et fonctions implémentées dans un DSP (Digital Signal Processing) extérieur. Le DSP peut alors faire varier la fréquence second synthétiseur indépendamment de la bande passante du filtre, décalant ainsi la bande passante audio sans faire varier largeur

La combinaison de largeur de bande programmable et de décalage programmable de la bande passante permet de régler les côtés supérieurs et inférieurs de la bande passante audio d'une manière indépendante. Il peut y avoir quelques résidus autour de la fréquence zéro, si le côté inférieur de la bande passante est réglé trop bas. Un filtrage additionnel dans le DSP peut éliminer ce résidu.

L'ajout d'un DSP peut permettre une grande collection de filtres passe-bande de largeurs et de centrages différents, avec un facteur de forme constant de 1.5. Ceci n'est pas réalisable avec des filtres analogiques. Pour cette étude, j'ai pour le moment opté pour la simplicité, et je n'utilise pas encore de DSP.

Il est fortement recommandé de se procurer la notice du HSP50016. Une des méthodes les plus simples est de la télécharger sur Internet

(http://www.semi.harris.com).

L'implémentation du second mélangeur, second synthétiseur et sommateur final est appelée « quadrature to real conversion ». L'explication mathématique est donnée dans la

mathématique est donnée dans la notice.

Le DDC nécessite 320 bits, répartis en 8 mots de 40 bits chacun pour le configurer entièrement. Cette programmation est très simple et sort du cadre de cet article. La notice est très complète et très facile à lire à ce sujet.

Notons que KC1HR a réalisé une interface de programmation qui permet de programmer le DDC à partir d'un PC, par la sortie imprimante.

Une horloge 50 MHz du commerce fonctionnant en 5 volts sert à produire le 25 MHz (division par 2 dans un 74S113) nécessaire au fonctionnement du CAN et du DDC.

La sortie série du DDC est appliquée à un CNA de 16 bits, le réglage numérique du gain s'obtenant en décalant le bit de données de timing du CNA, en utilisant implicitement le flot des bits série comme dans un registre à décalage de longueur variable. Pour utiliser cette fonction, le CNA doit avoir une entrée complémentée à 2, à la place d'une entrée offset-binaire. La sortie du CNA est transmise à un filtre passe bas à capacités commutées. L'horloge de ce filtre est la même qui est utilisée pour décaler les données vers le CNA. Ainsi la fréquence de coupure du filtre (1/100 de la fréquence d'horloge du filtre) est contrôlable depuis le DDC. Lorsque l'horloge est 38 fois le rapport d'échantillonnage du du CNA, fréquence de coupure du filtre est identique au côté supérieur de la bande passante du DDC.

La sortie du filtre est raccordée à un petit amplificateur BF par l'intermédiaire d'un filtre passe-bas analogique.

La réalisation n'est bien sûr pas parfaite. Il n'y a pas de CAG numérique. On peut envisager de contrôler l'overflow du CAN, et de commander un atténuateur à diodes Pin placé à la sortie du filtre d'entrée. Pour le moment, je n'ai pas jugé bon de monter un tel dispositif. Il faut dire qu'à part quelques essais décamétriques satisfaisants, récepteur est utilisé derrière convertisseur 144/ 10.7 MHz pour essais sur les satellites. C'est là où il va être intéressant de tester un tel dispositif, surtout pour décoder les communications digitales. Couplé avec un DSP Motorola (la carte

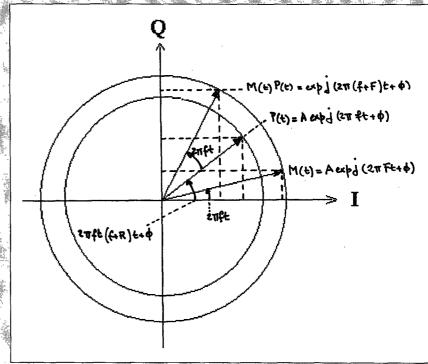

#### FIGURE 3

#### Représentation complexe du signal.

Conversion d'un signal complexe en signal réel.

EVM56002), il ne manque plus que P 3D en orbite pour s'éclater en programmant comme un malade, Hi ! L'écoute de la SSB est très confortable. Après avoir essayé plusieurs largeurs de bande, j'ai opté pour 2400 Hz, la bande passante à 2000 Hz est par trop étroite pour mes oreilles fatiguées. Quand aux graphistes, 400 Hz c'est le pied! mais l'ami KC1HR a réalisé un système avec un filtre de 107 Hz (décodage par ordinateur), pour la CCW. C'est là que l'on est heureux d'avoir en réception comme en émission des oscillateurs à commande numérique (il existe maintenant de tels circuits - à des prix très compétitifs - pour ce faire ; AD 7008 d'Analog Devices ou HSP 45102 d'Harris).

Il n'y a pas non plus de S-mètre. Mais c'est une mesure analogique ça ! Pour l'instant, je sais pas faire.

Et l'émission? C'est là que ça se complique un peu. Il n'existe pas encore de DUC (Digital Up Converter). Mais on peut s'en passer.

Le système Weaver est réversible : attaquer le DDC par un signal audio au lieu de la HF, programmer le générateur de phase pour 1.75 MHz, et on obtient une bande de base I et Q.

Ensuite, il faut augmenter le rapport d'échantillonnage des signaux I et Q jusqu'à un rapport d'horloge compatible avec la fréquence HF désirée, puis moduler une porteuse HF par les signaux I et Q.

Le HSP 50016 attaqué de cette façon sait sortir une bande de base I et Q convenable.

Un AD 7008 sait moduler sa porteuse par des signaux I et Q. Mais à l'heure actuelle l'échantilloneur-augmenteur de rapport n'existe pas. Il faut donc le réaliser avec une douzaine de circuits digitaux, et ce n'est pas évident. Ou confier le travail à un DSP (y-a-t-il un volontaire pour écrire le programme ?). Ce qui fait que je travaille sur une voie un peu différente qui marie DSP, circuits analogiques, filtres à capacités commutés, et bien sur un NCO pour finir. résultats actuels sont encourageants, mais I'OM n'a que 2 bras et une seule tête, et les journées ne font que 24 heures, et on ne peut pas les passer exclusivement, un fer à souder d'une main, et un clavier d'ordinateur de l'autre.

#### Modulations numériques

La modulation consiste à faire varier l'un des paramètres d'une porteuse afin de

transmettre une information. On peut agir sur son amplitude, sur sa phase, et même sur les deux.

Une modulation est d'autant plus efficace qu'elle permet de transmettre une grande quantité d'informations avec un étalement spectral réduit. Le débit d'une modulation numérique est exprimé en bits/s et en bauds, ces deux grandeurs n'étant pas toujours égales. On exprime en bauds le nombre de symboles transmis par seconde ; le nombre de bits représentés par un symbole dépend du type de modulation utilisé.

En transmission de données numériques, on trouve les types de modulation suivants

- ASK: modulation d'amplitude, absence ou présence de la porteuse.

- PSK: modulation de phase, déphasage de 0 ou de 180 degrés.

- FSK : modulation de fréquence de la porteuse.

- QPSK : variante de PSK, à 4 états.

- FFSK: variante de FSK, modems radio à 1200 bauds.

- GMSK : variante de FSK et de PSK, optimisée en occupation spectrale.

- QAM: modulation très puissante, agissant à la fois sur l'amplitude et sur la phase. 64 états maximum par caractères. Un récepteur numérisé peut traiter indifféremment les signaux en modulation analogique et en modulation numérique. Cette dernière est préférable car elle présente une très grande souplesse quant à la nature des données transmises, elle intègre des corrections d'erreur, ce qui constitue un avantage décisif.

# Représentation réelle et représentation complexe

Les nombres complexes sont un outil excellent pour la représentation des signaux modulés. La porteuse peut être représentée par un vecteur d'amplitude constante, en rotation constante à la vitesse angulaire 2f (rd/s). Le signal modulé peut être représenté par un vec

teur d'amplitude A, tournant à la vitesse angulaire 2(f+F) (rd/s), avec un angle initial égal à la phase (p). On peut imaginer les projections de ces vecteurs sur les axes réel et imaginaire du plan complexe (figure 3). Considérons une porteuse :  $p(t) = \cos 2 ft$  modulée par un signal

Ces signaux ont une représentation

$P(t) = \exp(i2ft)$

complexe:

= cos 2 ft + j sin 2 ft

$M(t) = A \exp(j2ft + p)$

m(t) = A cos (2Ft + p)

= A  $[\cos(2 ft + p) + \sin(2 ft + p)]$ Après passage dans le modulateur, on obtient :

- en représentation réelle:

$p(t) \cdot m(t) = A \cos 2ft(\cos(2ft+p))$

=  $(A/2)[\cos (2(f+F)t) + \cos (2(f-F)t)]$

- en représentation complexe:

P(t) M(t) = Aexp(j2ft) exp (2Ft+p)

$= A \exp j [2 (f+F)t + p]$

On constate qu'un signal modulé comporte 2 bandes latérales en représentation réelle, contre une seule en représentation complexe. Cette caractéristique sera utilisée avec profit dans les récepteurs numériques.

#### Conclusion

Avec l'arrivée de ces circuits intégrés et particulièrement du HSP50016, la numérisation des récepteurs est devenue très intéressante. L'obstacle majeur actuel est le prix de revient d'une telle réalisation. Il n'empêche que ce prix va très vite baisser, et nous allons voir fleurir dans les années qui viennent des récepteurs numérisés. La prochaine étape sera la description

de la réalisation personnelle. Vous verrez qu' au niveau du radioamateurisme, on peut réaliser quelque chose qui tienne la route, et qui soit un peu innovant. À vos fers à souder.

# Introduction à la radio numérique

Seconde et dernière partie.

## F5MI Jean-Pierre Mallet

La première partie de l'étude a permis de lever le voile théorique sur la radio numérique. Au travers de ma réalisation personnelle, nous allons voir ce qu'il est possible de faire avec des moyens amateurs.

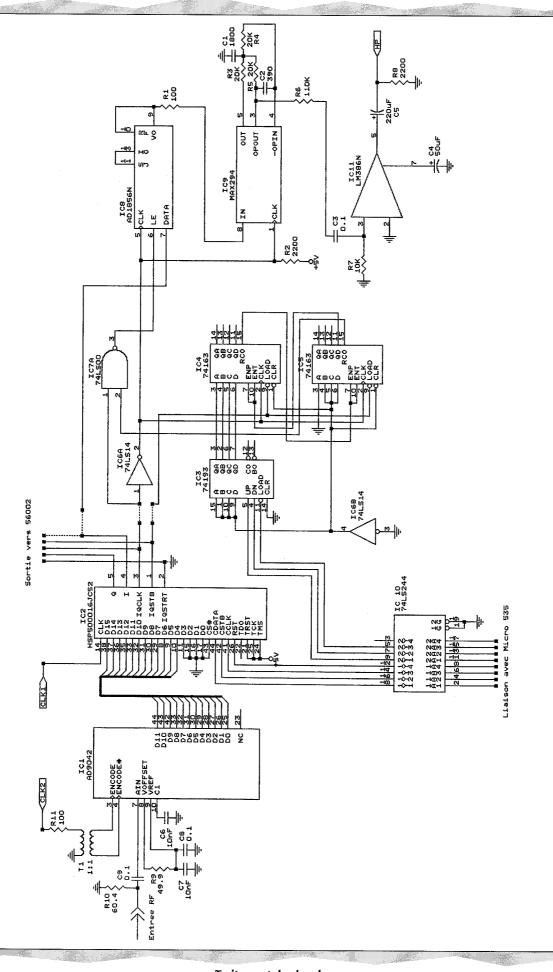

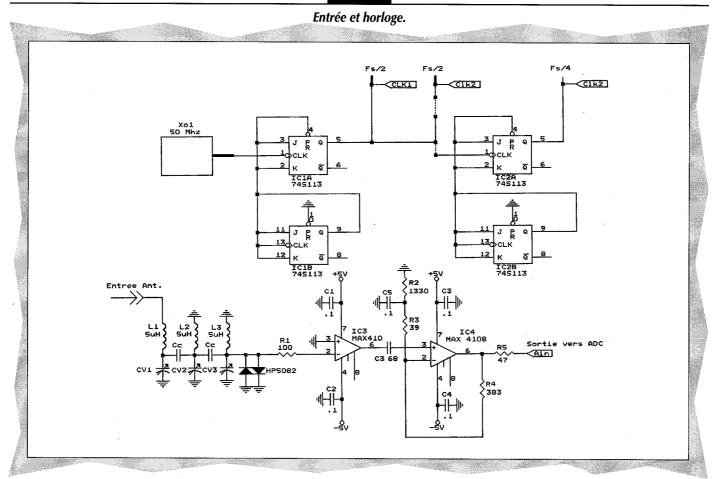

Les figures 1 à 3 donnent le schéma électrique de la réalisation. Il se compose de 3 parties : le module traitement du signal, le module entréehorloge, et le module microcontrôleur. Chaque partie est intéressante ; il n'y a aucun réglage à effectuer au moment de la mise au point, mais il ne faut pas croire que tout fonctionne par miracle. Le module d'entrée est très important : c'est lui aui conditionne les performances du système. Le filtre d'entrée accordable est nécessaire pour la sélectivité globale du récepteur. Plus grande sera la sélectivité à ce niveau, meilleure sera la conversion analogiquenumérique qui va suivre. Il faut bien comprendre une chose : c'est qu'au niveau de la conversion, si un signal unique est traité, le rapport signal/bruit sera optimal; tandis que si deux signaux sont traités ensemble, il faudra réduire le niveau de 6 dB pour éviter l'écretage en sortie, ainsi si 4 signaux sont traités il faudra réduire de 12 dB, de 18 dB pour 8 signaux, etc. Ce qui évidemment diminue d'autant le rapport S/B des signaux recus.

Le niveau de bruit plancher d'un CAN peut être déduit de l'équation suivante: Bruit plancher = 6.02d + 1.8 + 10 log (F(s) / (2 \* BW)), d étant la résolution (équation 1) Prenons un exemple concret : le CAN AD9042 peut être échantillonné par une

horloge de 40 MSPS (millions d'échantillons par seconde), soit une fréquence de 40 MHz.

Si l'on considère que le circuit d'entrée a une bande passante de 100 kHz, la réduction du bruit plancher au niveau du CAN sera de : 10 log (40 MHz /(2 \* 100 kHz)), soit 33 dB.

Comme l'on connaît la spécification du SNR qui est en l'occurrence de 67 dB, le SNR effectif pour un signal donné est alors:

6.02d+1.8+10log(F(s)/(2\*BW))

- HR (équation 2)

HR étant constitué d'une part par la réduction en fonction du nombre de signaux traités et d'autre part par la garde (headroom) que l'on doit conserver pour éviter écrétage et saturation. Cette garde peut varier de 3 à 15 dB. En pratique on prend 12 dB.

Transférons la valeur du SNR dans l'équation 2 à la place de (6.02d + 1.8). Avec 1 seul signal à traiter, le niveau du signal sera à 12 dB en dessous de la pleine échelle (garde = 12 dB) mais le SNR effectif sera de 67 + 33 - 12 = 88 dB. Avec 8 signaux à traiter le niveau des signaux sera à (18 + 12) = 30 dB en dessous de la pleine échelle, et le SNR effectif sera de 67 + 33 - 30 = 70 dB.

Et ainsi de suite... Échantillonner à une fréquence plus faible, 20 MHz par exemple, réduit le SNR effectif par canal. Par exemple, descendre F(s) à 20 MHz fait tomber le SNR effectif pour un seul canal de 10 dB; en compensation, le SFDR du CAN augmente sensiblement. Cet exemple simple montre l'attention qu'il faut porter au circuit d'entrée. Réduire la bande passante du circuit

n'est pas si intéressant que cela : le système s'accommode mieux bande passante large (au niveau du bruit s'entend), par contre diminuer autant que faire se peut le nombre de signaux à traiter est intéressant, et en OC cela par l'augmentation sélectivité, donc par la diminution de la bande passante! Il s'agit d'un compromis à trouver. Si le système numérique ne sert que de FI au récepteur, il est évident que nous nous trouverons dans le cas d'un monocanal, et que le filtre d'entrée ne servira qu'à fixer la bande passante globale du récepteur, qui pourra atteindre 6.5 MHz dans le cas de réception d'images de télé numérique.

J'ai opté pour un circuit d'entrée à accord variable : à l'usage, cela donne satisfaction. On peut également construire des filtres d'entrée à bande passante fixe comme on en rencontre dans les récepteurs décamétriques.

Les deux amplis qui suivent le filtre ont pour but d'amener le signal au niveau nécessaire pour la conversion analogique numérique. Ici on est à large bande; on aurait pu utiliser des composants discrets, mais au prix de nombreux circuits annexes (selfs, transfos, etc.) que j'ai voulu éviter. J'ai surtout utilisé les qualités de ces amplis, qui sont, d'une part, une bande passante très plate (400 MHz à - 3 dB pour le MAX 4108), un SFDR de 81 dBc à 20 MHz, et d'autre part, un bruit très faible (0.75nV/racine(Hz)). Le gain des 2 amplis est suffisant dans tous les cas de figure ; il est réglable par modification résistances, c'est-à-dire simplement. On obtient environ 40 dB. Le convertisseur ne comportant

pas de sortie de dépassement, il est difficile de savoir si le niveau des signaux d'entrée est suffisant.

Comme je l'ai déjà dit dans la première partie, il n'y a pas de CAG; si les signaux sont trop importants, on peut insérer des atténuateurs dans l'entrée antenne! Les essais ont montré qu'ils n'étaient utiles que pour l'écoute de la radiodiffusion sur la bande 40 mètres! Mais ce n'est pas le but recherché, loin de là.

Le convertisseur analogique-numérique utilisé est un modèle plastique de chez Analog-Devices, le AD9042 ; c'est un convertisseur monolithique 12 bits fonctionnant à 41 MSPS. Son SFDR est de 80 dB, il est alimenté en 5 volts et sa dissipation est de 595 mW, ce qui veut dire qu'il va chauffer ! Comme il est livré en PLCC 44, la première chose à faire sera de bien le coller contre la plaque de circuit imprimé, la deuxième de lui coller un petit radiateur à l'instar des PGA d'Intel (ØjA = 55°C/W).

La sortie des données est complémentée à 2.

Le circuit d'horloge est classique. À partir d'une horloge de type IQXO et de fréquence 50 ou 40 MHz, on obtient soit 25 MHz soit 20, soit 12.5, soit 10 MHz

après passage dans un diviseur rapide. Alors pourquoi tout cela ? Le Subsampling!

J'ai déjà touché un mot de cela dans la première partie. Le critère de Nyquist dit que les convertisseurs nécessitent un rapport d'échantillonnage au moins double de la plus haute fréquence à recevoir ; c'est-à-dire, avec une horloge à 50 MHz, une zone allant de 0 à 50/2 = 25 MHz, 20 MHz avec 40 MHz, etc. Ceci s'appelle l'échantillonnage en bande de base. La bande de base de l'AD 9042 est de 20 MHz. Comment faire alors pour recevoir un signal de 21.4 MHz?

Le premier critère de Nyquist va de 0 à F(s)/2.

Le deuxième critère va de F(s)/2 à F(s). Le troisième critère va de F(s) à 3/2 F(s), etc.

Si est F(s) est à 20 MHz, la première zone se trouve de 0 à 10 MHz, la seconde de 10 à 20, et la troisième de 20 à 30 MHz. La solution est d'échantillonner un signal qui se trouve dans la troisième bande de Nyquist, en accordant le DDC qui suivra sur une fréquence telle que F = (2 \* F(s) - Fsignal), soit dans ce cas : F = 2\* 20 - 21.4 soit 18.6 MHz.

On peut voir également que si on choi-

sit F(s) = 10 MHz, on obtient comme résultat 2 \* 10 - 21.4 = - 1.4 MHz, ce qui signifie que la bande sera renversée.

Le convertisseur fournit en sortie ces fréquences qui sont des alias ou des fréquences symétriques.

Subsampling est à utiliser précaution, faute de ne plus savoir sur quoi on s'accorde. Le maximum de complexité est obtenu lors de réception d'un signal de 45 MHz, avec une fréquence d'échantillonnage de 4 MHz. Il va y avoir des alias sur le spectre tous les 4 MHz et le 11e (4 \* 11 = 44) tombe à 1 MHz de 45 MHz. L'accord du DDC sur 1 MHz permet la réception, mais l'accord sur 5 MHz aussi etc. ! Le filtre anti-alias s'impose, et le calcul aussi, car s'il tombe des alias dans la bande passante du récepteur, vous pouvez vous préparer à une sérénade d'oiseaux! Avec les fréquences utilisées ici et les sélectivités étroites adoptées, il y a peu de chance que l'on arrive à de telles extrémités. La réception du 21 ou du 28 MHz est très possible en installant les filtres convenables à l'entrée, et en se rappelant au moment venu de retourner la bande.

Ce module a été réalisé sur epoxy 16/10e

#### FIGURE 2

de millimètre, en double face, l'une des faces servant de plan de masse, et de refroidisseur annexe! Des précautions ont été prises afin de filtrer l'horloge au maximum, pour éviter des cohabitations délicates. Le circuit à été entièrement enfermé dans un boîtier en fer blanc (Schubert), les connexions se faisant par subclip et par bande souple pour les sorties numériques. On remarquera que l'horloge est symétrisée: un transfo 1:1 fera l'affaire. Il est plus élégant d'utiliser un transfo que de câbler le circuit en dissymétrique.

Cette configuration a été choisie afin de pouvoir tester différentes têtes avec les mêmes modules, ce qui n'aurait pas été le cas si un seul circuit avait été réalisé. Le module de traitement est le cœur du système. Ici, c'est de la microinformatique, car le câblage ne posant aucun problème - j'ai repris l'étude de KC1HR Peter Anderson - tout va se régler par une communication homme-machine. Le HSP50016JC-52 peut être échantillonné à 52 MSPS, son SFDR est > 102 dB, il accepte 16 bits à l'entrée, sa résolution en fréquence est < 0.006 Hz, II possède 2 filtres identiques pour les canaux I et Q, l'ondulation dans la bande passante est < 0.04 dB, l'atténuation hors bande est > 104 dB, le facteur de forme du filtre entre -3 dB et - 102 dB est < 1.5, la décimation varie de 64 à 131.072.

Il est alimenté en 5 volts, sa dissipation maximum est de 2.28 W (ØjA = 35°C/ W). Sa consommation est fonction de la fréquence, elle est de 7.5 ma/MHz. Le montage sur le circuit doit être soigné, il doit être collé contre l'époxy, et un radiateur du style PGA lui est adjoint. Il n'y a pas lieu à ventiler, mais une ventilation naturelle de l'air chaud devra être prévue; ce qui veut dire que l'enfermer dans un boîtier étanche n'est pas conseillé . IC3, IC4 et IC5 servent à un réglage de gain numérique. IC3 compteur 4 bits up-down - mémorise l'échelon de gain programmé à partir du microcontrôleur et fournit 16 échelons de gain. Le DDC est programmé pour sortir environ 38 cycles de IQCLK par échantillon N/A, la sortie série des données du DDC est programmée à 32 bits. IQSTB est programmé pour être à 1 pendant la durée des 32 bits et à 0 pendant les 6 cycles restants. Le CNA a besoin d'une impulsion LE à la fin d'un mot de 16 bits. Le gain varie en faisant varier les 16 bits (sur les 32 sortis) chargés dans le convertisseur N/A. Ceci est réalisé en faisant varier le retard entre

le front montant de IQSTB et l'impulsion LE.

Le gain est minimum lorsque premiers 16 bits sont utilisés, données sont envovées MSB en premier. Si le retard augmente, des bits moins significatifs sont utilisés. augmentant le gain de 6 dB par échelon. Cette fonction réalise le fait que dans un entier complémenté à 2, exprimant un petit nombre, les bits d'ordre élevés sont soit tous des 0, soit tous des 1, dépendant du signe de l'entier.

IC4 et IC5 sont câblés en compteurs 8 bits up-synchrone. Lorsque IQSTB est à 0, IC4 et IC5 sont chargés par l'échelon de gain désiré, quand IQSTB passe à 1, IC3 et IC4 comptent jusqu'à leur valeur maximale, tout à 1, puis, comptent un peu plus et s'arrêtent dès que IQSTB repasse à 0. La sortie 15 de IC5 est à 1 seulement lorsque le compteur à atteint sa valeur maximale. La porte NAND U7 convertit l'impulsion issue de IC5 broche 15, en impulsion LE pour le CNA.

Le CNA est un convertisseur 16 bits du même type que ceux utilisées dans les lecteurs de disques numériques, sa pleine échelle est de ± 3 V crête.

Le circuit Maxim MAX294 est un filtre passe-bas à capacités commutées, avec un rapport entre l'horloge et la fréquence de coupure du filtre de 100. Il a un facteur de forme de 1.2 à - 58 dB d'atténuation hors bande. IQCLK est programmé de façon à ce que la fréquence de coupure de ce filtre soit la même que celle du filtre du DDC.

La partie ampli-op du MAX294 est utilisée comme passe-bas pour éliminer le bruit d'horloge présent à la sortie du filtre.

Un petit ampli ajoute 6 dB de gain audio pour attaquer un casque ou un petit haut-parleur.

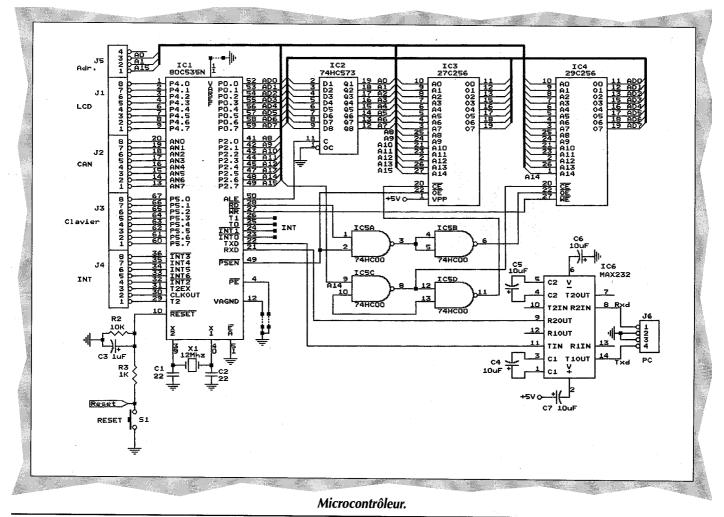

Le troisième module est un microcontrôleur réalisé autour d'un micro Siemens 80C535 cadencé à 12 MHz. Ce micro a les caractéristiques suivantes

- 256 octets de RAM interne.

- 6 ports parallèles de 8 bits.

- Interface de communication série fonctionnant sous 4 modes.

- 3 compteurs temporisateurs de 16 bits

- Fonction rechargement, capture et comparaison sur 16 bits pour au moins 1 de ses compteurs.

- CAN associé à 1 port de 8 entrées de type analogique, référence de tension programmable.

- 1 temporisateur 16 bits dédié à la fonction chien de garde.

- Processeur booléen du 8051.

- · 256 bits adressables directement.

- 12 sources d'interruption (7 ext., 5 int.) à 4 niveaux de priorité.

- Boitier PLCC 68 broches.

Une mémoire EPROM de 32 x 8 K (27C256), associée avec une EEPROM identique (29C256) permet de stocker le programme et toutes les données qui pourront être chargées dans le DDC.

Un circuit MAX232 permet la liaison avec un PC, pour des dialogues divers. Un afficheur LCD à 2 lignes de 16 caractères permet de visualiser les diverses informations qui sont envoyées par le programme. Fréquence, gain, bande passante, etc.

Un clavier hexadécimal câblé en Matrice 4 X 4 permet le dialogue homme - machine.

L'implantation est réalisée sur une carte époxy 16/101 classique de dimensions 110 x 75 mm,

Les sorties se font par des limandes classiques.

#### Programmation du DDC

Sans entrer dans les détails, je vous propose de passer en revue la programmation de ce circuit.

Le DDC se programme au moyen de 8 mots de contrôle de 40 bits, numérotés de 0 à 7

Les 3 premiers bits de chaque mot de contrôle sont les adresses des mots de contrôle.

Les mots de contrôle doivent être émis le bit MSB en premier.

Les mots 0 et 7 ne sont pas utilisés ici. Le mot 0 sert à « Updater » le registre de contrôle, et le mot 7 est une procédure de test spéciale.

Le mot 1 sert à programmer le générateur de phase et à valider tous les changements qui auraient été effectués dans les autres mots. Il est évident qu'il devra être entré en dernier.

Il sert à entrer la fréquence sur laquelle le récepteur devra être accordé. J'ai donné dans la première partie la formule à utiliser dans ce cas-là.

Les mots 2 et 3 servent à programmer le générateur de phase pour des modes particuliers, on ne les utilisera pas, des zéros seront envoyés pour les mots considérés.

Le mot 4 sert à programmer la sortie. On mettra le mode réel (Up Convert by f"/4) bits 32-31 à 01, le décalage HDH interne bits 6-1 à 010100, et Indiquer si la sortie est spectralement inversée bit

#### FIGURE 3

O à 1. Ce bit doit être à 0 pour une réception USB, et à 1 pour une réception LSB (comme ici on travaille en dessous de 10 MHz, il sera à 1).

Le mot 5 sert à programmer la largeur de la bande passante bits 35-21, le multiplicateur de gain bits 20-5, et le format de la sortie bits 4-0.

La notice donne des équations simples qui permettent de calculer les rapports de décimation à entrer pour des largeurs de bande diverses. En ce qui concerne la sortie, les formats disponibles sont 16, 32 ou 38 bits fixes et 32 bits flottants IEEE. les sorties fixes peuvent être compléméntées à 2, offset binaire ou signées. La sortie série peut être conditionnée avec le bit MSB en premier ou bien avec le bit LSB en premier.

J'ai utilisé ici la sortie complémentée à 2, en 32 bits, avec le bit MSB en premier. Le mot 6 contrôle tous les formats.

Format et polarité de IQCLK, emplacement et polarité de IQSTB, et polarité des données de l'entrée et de la sortie.

Ce récepteur utilise IQCLK fonctionnant continuellement à 38 fois le rapport d'échantillonnage du CNA, avec les don nées stables lors de la retombée de IQCLK.

IQSTB est mis à 1 pendant la sortie des données et à 0 le reste du temps.

L'entrée est en complément à 2 pour s'adapter au format de l'AD6042.

KC1HR a réalisé une interface très simple, permettant de relier le DDC à un PC par la prise Centronics. Un programme en C permet de commander les divers contrôles du chip. Si un OM est intéressé je lui communiquerai tout cela (j'ai adapté le programme à mes besoins).

J'ai préféré une interface à partir du microcontrôleur, ce qui libère le PC pour d'autres tâches. Il ne faut pas oublier que je peux réunir la carte à un DSP 56002 pour des traitements beaucoup plus exotiques, et que là j'ai besoin du PC. On ne peut pas transformer le shack en labo du Docteur Jekyll, avec de nombreux PC travaillant chacun dans son coin à une quelconque besogne obscure

Je signale que le Basic du 8052 est disponible en format hexa sur Internet. Il est facile de le graver sur une EPROM et de s'en servir sur la carte microcontrôleur.

Le programme va soit en RAM pour la mise au point, soit sur une EEPROM pour l'utilisation. C'est facile à utiliser depuis le PC, pour tester le fonctionnement du circuit, si on est allergique aux langages de haut niveau.

Pour mon compte la programmation se fait en assembleur. L'EEPROM sert à stocker une grande quantité de choses, en particulier de nombreux formats de filtres que l'on peut charger dans le DDC à la demande.

Et qu'est ce que cela donne en bout du compte ?

J'ai donné dans la première partie des résultats à 10.5 MHz : ils ont été obtenus avec une tête un peu différente, qui comprend un filtre monolithique de 30 kHz de bande passante, précédé et suivi d'un ampli MAX 4108.

J'ai indiqué un MDS (signal détectable minimal) de - 130 dBm avec une gamme dynamique de 72 dB; le microvolt passe avec un rapport signal/bruit de 20 dB. À 3.5 avec la tête décrite ici on obtient un MDS de - 128 dBm et une gamme dynamique de 57 dB, le blocage apparaissant à 90 dB. Ce qui veut dire que les

décodage automatique par un microordinateur, mais cela sort du cadre de l'étude pour le moment.

Au point où j'en suis de l'étude, le système sert de FI 21.4 MHz derrière un convertisseur 435 MHz pour l'écoute des satellites. J'ai un programme DSP qui commence à tourner sur un 56002 et qui décode le BPSK à peu près correctement. Là cela devient très intéressant, surtout lorsqu'il s'agit de contrôler la dérive du satellite.

Il m'a été soumis le cas du spectre étalé. En principe c'est réalisable, il faut se pencher sur une future réglementation qui nous serait imposée pour d'éventuelles expérimentations.

Mon adresse PK est F5Ml@F1PKl.faqi. fra.eu. Je répondrai à toute question qui me sera posée sur ce récepteur, soit par courrier, soit via packet.

signaux supérieurs à S9 vont commencer à distordre ! En réalité, le jour tout se passe bien, le soir, un atténuateur de 20 dB règle les problèmes (je parle ici de S9 réel, c'est-à-dire 50  $\mu$ V/50 ohms ou -74 dbm).

Ces mesures sont difficiles à réaliser : il faut faire des mesures de distorsion en BF et savoir si les distorsions ou écrétages proviennent ou non de la partie audio. je ne ferai pas un procès à celui qui me démontrera que j'ai fait des erreurs de quelques dB (en quel sens ?).

Et à l'oreille ? Le souffle est très faible, c'est indéniable, les signaux sont très écoute corrects. leur est très confortable - j'ai dans le programme un système qui me permet de déplacer les filtres par bonds de 100 Hz en appuyant sur 2 touches (+ et -). En fonction des stations entendues, le confort est excellent. L'intermodulation nettement supérieure à ce que donne un récepteur classique, cela se sent sur les bandes encombrées comme le 80 mètres le soir. L'écoute de la CW est bien plus intéressante qu'avec un récepteur analogique. Cela tient à 2 l'incroyable stabilité récepteur, et des filtres CW assez délirants. On peut envisager un